PathWave Advanced Design System (ADS) 2023 Update 2 (x64)

Free Download PathWave Advanced Design System (ADS) 2023 Update 2 | 6.4 Gb

Keysight Technologies, Inc., a leading technology company that delivers advanced design and validation solutions to help accelerate innovation to connect and secure the world, has released update 2 for PathWave Advanced Design System (ADS) 2023. This update ncludes new capabilities and enhancements for RF/MW, High Speed Digital, Power and Quantum Electronics in Python automation, design management, layout, data display, verification, circuit-EM simulation, high-performance-computing (HPC) and license queuing.

Product:PathWave Advanced Design System (ADS)

Version:2023 Update 2

Supported Architectures:x64

Website Home Page :www.keysight.com

Languages Supported:english

System Requirements:Windows & Linux *

Size:6.4 Gb

Advanced Design System 2023 Update 2.0 - Release: 2023-03-31

Design & Tech Management

General

- (Alpha Feature) The Python console is available in ADS. ADS has a Python console accessible from a new top-level 'Python' menu that will allow users to use Python to control workflow, modify workspaces, automate tasks and customize the user interface. The Python console can be activated by launching ADS with an additional command line argument: "ads.exe -python". In this alpha release, users can use the console for general Python programming; however, only a limited set of APIs is available for controlling workflow, modifying workspaces and customizing the user interface. More APIs will be made available in subsequent ADS releases. Note that these APIs are subject to change until this feature reaches production release.

- Added capability for cleaning up the simulation log files in a workspace's data directory using the Cleanup Workspace.

- Improved the entry method for specifying Unarchive destination path. The recent destination paths are listed in the Unarchive destination path field and can be selected for reuse.

- Enhanced ADS Installer for supporting Windows multiuser systems. The HOME setting configured by the ADS installer on the Windows system is refined to better support multiuser systems.

- Enhanced support for dependent files in Version Control. Improved Include Hierarchy option to also list dependent files to the check in and check out list.

- Enhanced Version Control plugin interface for allowing extra command line options. Additional command options can be passed to the version control tool when files are checked in, checked out or tagged.

Design Editing and Layout

General

- Added ability for changing via type for multiple vias. Properties Editor has been enhanced to support editing of multiple selected PCb Vias that are Via Rule based.

- Enhanced the GUI performance of presenting large number of stacked Vias. When there exists a large number of stacked via combinations, the new Select Via Rules dialog box can be invoked to help manage the via selection process. For more information, refer to Insert a Stacked Via documentation.

- Improved support for concurrent design editing done by multiple users. The following highlights several enhancements for improving design editing done by multiple users concurrently:

. New option for opening a design in read-only or editable mode

. New provision for changing the mode for an already opened design

. Push Into command offers two modes: Push Into Hierarchy Read and Push Into Hierarchy Edit.

. Several new AEL APIs added to support opening a design in read-only or editable mode:

de_get_design_context_from_name()

de_find_design_context_from_name()

de_push_into_instance_readonly();

de_push_into_instance_editable();

Design Import/Export

- Additional AutoCAD formats supported. In DXF/DWG export, the set of supported AutoCAD versions for the output file is expanded to include AutoCAD 2010, 2013, 2018 compatible formats.

Ground Plane

- "metal degassing" is supported. The Create and Edit Plane dialog comes with added functionality for degassing.

- Removing "islands" is supported. The Create and Edit Plane dialog comes with added functionality for removing pieces of metal (islands) that have become disconnected from a ground plane net. Users may specify that all islands or islands smaller than a specified area are to be removed when creating or regenerating a plane. For more detailed information, refer to Creating a Plane and Editing a Plane documentation.Corresponding AEL API's have been provided to the Plane Functions API set:

db_set_plane_remove_islands_mode()

db_get_plane_remove_islands_mode()

db_get_plane_remove_islands_area()

AEL Interfaces

- Added new AEL function for creating stacked PCb vias based on stacked via rule. For more information, refer to db_create_stacked_pcb_via().

- AEL functions for retrieving the details of a stack via rule. The following new AEL APIs are for querying or updating stacked via rules:

db_stack_via_rule_is_enabled()

db_stack_via_rule_get_priority()

db_stack_via_rule_get_start_layer()

db_stack_via_rule_get_stop_layer()

db_stack_via_rule_get_via_names()

db_stack_via_rule_set_enabled()

db_stack_via_rule_set_priority()

db_split_net () returns the nets created by the split. For more information, refer to db_split_net().

AEL function for getting a list of via stack definitions. For more information, refer to db_get_stack_via_rule_names().

Interconnect, Connectivity and Pin

- New Layout Connectivity is on by default. The Layout's Net-based and WYSIWYG connectivity modes are deprecated. Layout's new connectivity behavior will no longer place objects on a net by default. Objects with no net will still automatically be placed on the net of a touching object if edited to touch said object.

- Added new option for assigning nets in ADS GUI. A new option for assigning nets to objects without a net is added to the Layout Tools menu. A new AEL function, db_assign_nets_to_objects_in_layout() is also available for the same functionality.

- An error is issued if netlisting a layout containing instance terminals on "no net". For more information, refer to New Connectivity documentation.

- Removed the option of forcing an object to a net in layout.

- Deprecated an option of creating wires when detaching objects. Deprecated feature to automatically create wires between components when separating objects in Layout and generating a Layout from Schematic.

- Enhanced trace routing for picking up the net of the touching objects.

Quantum

General

Five different quantum design flow examples are added as follows:

- Superconducting Qubit

- Four Superconducting Qubits

- Basic Quantum Amplifier

- Uniform JTWPA

- Floquet JTWPA

Quantum Layout

A library of quantum layout components is added. The library contains the following components:

- Capacitor-N-Interdigital: Q_CapacitorNInterdigital

- CPW Coupler-T: Q_CpwCouplerT

- CPW Centered Coupler-T: Q_CpwCouplerTCenter

- CPW Curved Bend: Q_CpwCurvedBend

- CPW Launchpad: Q_CpwLaunchpadWirebond

- CPW Line: Q_CpwLine

- CPW Meander-Line: Q_CpwMeander

- Abstract Inductor: Q_InductorAbstract

- Transmon Cross: Q_TransmonCross

- Transmon Pocket: Q_TransmonPocket

- Automatic airbridges are added to the CPW lines and meander-lines

- Quantum technology is added to the layout technology wizard for new workspaces

- GDS exporting for quantum layouts is added from Tools → Quantum → Export to GDSII

Installation

General

- Install Python wheels to a "wheelhouse" directory. Python wheels that were previously provided in $HPEESOF_DIR/tools/python/packages are now located at $HPEESOF_DIR/tools/python/wheelhouse.

Circuit Simulation

General

- The latest BSIM-IMG 102.9.6 is now supported.

EM Simulation

RFPro

- An RFPro addon is now available to open the Ltd substrate editor.

- Vendor-licensed and encrypted EMPro 3D component can be placed in an ADS layout or natively imported in RFPro and be simulated with RFPro-FEM Generation 2 when the vendor license is available.

- The frequency plan provides new controls for the s-parameter and field data storage.

. When designated as 'Simulated', the simulator will compute and store every frequency of the plan. This corresponds with the behavior in previous releases. Fields for these frequencies will be stored if the entry is On.

. When designated as 'Interpolated', the simulator will perform an adaptive sweep, but in a postprocessing step, the rational model will be sampled in the frequencies defined by the plan. No fields will be stored.

- In case no explicit pin reference is known, the nearest 'Reference Pin on Layer' will be used when creating a port.

- Assemble designs from different technologies directly in RFPro. When you enable 'Show Beta Functionality' on the General tab of Tools > options... dialog, you can select File > Import > OA Layout... to insert a component designed in one technology, place that next to a design with a different technology, and simulate the assembly with the FEM Generation 2 simulator.

Momentum

. Pilot release for a new thick conductor defined between dielectric interfaces in the substrate stack. It allows to define a conductor that is as thick as the adjacent dielectric layer.

. Set SUBED_ENABLE_THICKCONDUCTOR=1 in your environment before launching ADS, Virtuoso, or Custom Compiler! That will allow you to define such conductor in the .subst and/or .ltd substrate editor.

HSD

General

- New progress/status bar and multithreading for calculating S-parameters with new reference impedance in S-Parameter Toolkit.

- Supports units for CTLE and CDR in AMI Model Builder.

- Design Cloud remote simulation options -job-type=com.keysight.ads.emsetup and -job-version=

- xxPro Analyses results "Generate Test Bench Schematic" now generates a schematic with "Component Model Group Names" next to the component instance for easier navigation.

Memory Designer

- Supports IBIS BIRD 178, "Executable_Rx and_Tx" sub-parameters.

- Supports forwarded clock for PAM-n modulation.

- Enhancement to HTML report generation:

. HTML report generation with an existing dataset without re-simulating the design.

. An HTML report can be created with measurement results sorted either by signals or by measurements.

- Supports S-Parameter simulation with Memory Designer.

SerDes Design

- COM calculation with S-parameter files (THRU, NEXT, and FEXT files).

EM - SIPro

- Causality enforcement for SI simulation S-parameters (beta feature). With beta mode enabled, SI simulations will produce S-parameters (in the form of .sio files) that are improved in terms of causality and quality of data in the low-frequency range.

- To benefit optimally from this new feature, the resulting S-parameter files should be used in Snp components with the Interpolation method set to 'Cubic spline' and the interpolation domain set to 'Rectangular'.

- Especially for verification in the causality check of the ADS S-Parameter Toolkit, a dense enough resampling with these interpolation settings should be used.

- Improved the computation time of PaSi simulations by 25%.

EM - PIPro

- ADS PIPro DC and Conducted EMI now handle cascaded VRMs where one switching VRM supplies the next switching VRM.

- New ODB++ version 8.1 compatible importer with improved handling of PCB stack-ups. (Available as a Beta Feature)

- New IPC-2581B PCB importer (beta feature).

- PIPro Component Loop Inductance report now handles AC analysis swept parameters.

Verification

Layout Versus Schematic

- LVS support for parameterized sub-circuits is improved.

Design Rule Checker

- DRC rules compiler reports a syntax warning for unsupported usage for the case where a polygon or edge selection rule is used outside a dve_drc() statement.

Electrical Rule Check

- ERC supports configuring and running jobs from an AEL script.

- ERC current density calculation includes layer thickness.

Power Electronics

Power Electronics Model Builder Tool

- Added IGBT model extraction.

Power Electronics Library

- Added step failure recovery mode in TransientPE controller to improve transient convergence on switching circuits.

Netlist Translator

- Added Tikf, the linear temperature coefficient of Ikf to diode model.

Examples

- SMPS Performance test bench(transient recovery and efficiency) for DC-DC converter.

Data Display

General

- Added capability for Importing/Exporting grouped limit lines and masks. Grouped limit lines and masks can be saved to an external file and loaded back into DDS for reuse. For more information, refer to Import/Export specification documentation.

- Improved the performance of opening .dds file. Calculation of equations during file open are deferred when possible.

- Added capability for automatically calculating new step size when changing axis min and max.

- Added capability for group reordering of traces in Description Traces & Attributes options dialog box. Use multiple selections of traces to reorder them in the Description together.

- Datalink is packaged with ADS installer. Datalink is no longer a separate ADS add-on; instead it comes with ADS installer. At run-time, it uses the python installed by ADS. In addition, Spyder has been replaced with Visual Studio Code.

- Datasets can be saved while they are in use by DDS or Python interface. Also, a new button in the toolbar is available for recalculating Descriptions and Equations after a dataset is updated.

Data Viewing & Analysis and Manipulation

- Added an AEL function for generating a textual output of a dataset variable. For more information, refer to dump().

- Datalink: VS Code is the default editor for Datalink script.

- Enhanced VS Code for debugging dataset and equation variables. When debugging measurement equations in VS Code, the contents of HPVar related to those equations can be viewed in the Variable and Watch windows.

- Enhanced VS Code for debugging List type variables using an expandable view in Variables list.

- The interpolate() function supports multi-dimension parameters. For more information, refer to interpolate().

Design Cloud

General

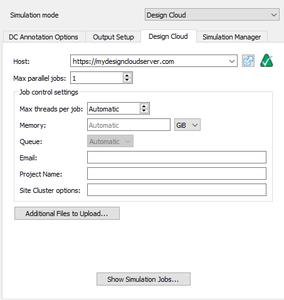

- DesignCloud ADSSim: New Resource GUI to set threads, memory, email, and project name for controlling site cluster options easily. The new resource GUI is currently hidden behind a feature flag. To enable it, the user must set the flag on the terminal as specified below before starting ADS.

ENABLE_NEW_RESOURCE_GUI=TRUE

The new resource GUI would allow users to specify:

. Max threads per job

. Memory

. Project name

- User can save username and password in the design cloud authentication window. An option is added to store credentials for Design Cloud:

. On Windows, this option will store the credentials in the Credential Manager.

. On Linux, this will store the credentials via the Secret Service API in the user's keyring.

Design Editing and Layout

General

- Fixed trace snapping so that it would not snap to traces that are not on the same layer as the trace being worked on.

- Flattening artwork command preserves teardrops in traces. Flattening command will no longer, under any condition, convert TRACE to PATH. If connectivity needs not to be preserved, then trace with NO NET will be created.

Design Import/Export

- Gerber export can export Drill files alone. Fixed a defect that prevented drill files from being created unless their corresponding Gerber layers were also selected in the Gerber/drill export options dialog. It is no longer necessary to select Gerber layers in order to create drill files, a drill layer selection is sufficient.

- The actual shape's arc resolution value is now used during DXF export when faceting polygons with holes if the "holes as cutlines" hole format is chosen.

AEL Interfaces

- Fixes are integrated to two path-related AEL APIs.

db_set_path_endcap() supports three endtypes for path DB_SQUARE_CAP, DB_ROUND_CAP, and DB_SQUARE_CAP_THAT_EXTENDS_HALF_width.

db_set_path_corner() supports three corner styles for path DB_MITERED_CORNER, DB_SQUARE_CORNER, and DB_CURVED_CORNER.

Design & Tech Management

General

- Enhanced VS Code AEL Debugger - can debug a function using optional argument.

- iPDK Python: ADS crash opening layout for attached workspace .

Circuit Simulation

General

- A bug has been fixed when using some voltage dependent capacitor models in Spectre language.

ElectroThermal

- Annotation of power onto non-leaf instances must be explicitly enabled:

- The environment variable ADS_ETH_ENABLE_PARENT_POWER_CALC, if set to 1, causes the power of devices within a model to be summed and annotated onto the parent instance of those devices. This is useful when the parents instance-name is used to identify a heat-source, but power is only reported on lower level (child) devices.

- If ADS_ETH_ENABLE_PARENT_POWER_CALC is not set (which is the default) or is not 1, then the annotation described above does not occur.

- Note that beginning in ADS2022 until this release the environment variable ADS_ETH_DISABLE_PARENT_POWER_CALC was used for the same purpose (with the opposite settings). However, it enabled the computation described above by default. This behavior is now reversed, as it is not consistent with PDKs built before the current release.

EM Simulation

Momentum

- Edge mesh and transmission line mesh seeding on the side walls of thick conductors are preserved in the mesh reduction process

- Fix in the resistance modeling of thick conductors with sheet model

- Improved topology for the current modeling at the contacts between vias and conductors

RFPro

- To workaround a crash in Microsoft's mimalloc library on application startup on windows 11, set the following environment variable MIMALLOC_DISABLE_REDIRECT=1. Performance may be degraded if this redirect is disabled. Remove the variable once Microsoft releases a fix in its mimalloc library.

- The schematic view generation swaps a pipe character in port names with an underscore yielding correct named connections.

- A bug was fixed in the netlist code of 'empro_basic:em_pnport' component. This cdf-based component will netlist in the spectre syntax as expected by the platform.

- An RFPro performance issue has been addressed when a design refresh is triggered while the S-parameter results window is open.

- The 'Create script' context menu is now functional for Near and Far Field Results.

- An issue has been fixed that could prohibit near or far field visualization even though the field storage was enabled.

- An issue has been fixed that incorrectly flagged a project as modified when re-running an analysis.

- When making a view translucent (opacity < 100%), edges and dielectric parts are hidden for performance reasons. Returning to a 100% opaque view now restores visibility.

- An issue has been fixed that prohibited to copy and paste a frequency plan.

FEM

- An issue in the FEM simulator has been fixed that cause a simulation failure with an 'expired token' error.

- An issue has been fixed in the RFPro-FEM Generation 2 simulator that lead to an open circuit behavior in case of a port with pin shapes on multiple layers.

- An issue has been fixed in the RFPro-FEM Generation 2 solver that caused a mesh failure for a smart-mounted SOI chip on a laminate.

- An issue has been fixed in the RFPro-FEM Generation 2 solver that caused a mesh failure for a package mounted on a PCB using nested technology.

- An RFPro-FEM simulation bug has been fixed that incorrectly used the mesh refinement frequency.

EM Integration

- The dataset generation at the end of an EM Setup-FEM simulation of a design with a large number of ports is much faster.

- An EM Setup issue has been fixed that prohibited simulations of a layout containing waveguide walls.

- FEM simulations run properly now on simulation directories with non-ASCII characters.

HSD

General

- PCIe Reference Channel does not include a typical AIC loss of 9.5 dB. Inclusion of missing AIC loss of 9.5db reference channel.

- ODB++ import bug fixed for missing component pins when designs also contain mechanical tooling hole components.

EM - PIPro

- PIPro PDN impedance and S-parameter Descriptions now provide a warning if a component model is outside of the available frequency range.

- ADS2023U1.x Pipro DC analyses .docx or .html generation getting stuck has been fixed.

- PIPro Thermal and Electrothermal analyses now default to not using a thermal pad to avoid invalid setups when components have no metal underneath them.

- PIPro AC and Conducted EMI improved handling of pin port definitions when landing on non-circular vias.

- Improved handling of multi-pin components when calculating loop inductances in PIPro AC Analysis results.

Memory Designer

- Missing units for reserved parameters in AMI modeler (Tx and Rx). Added units for CTLE, Rx_Noise, Rx_Receiver_Sensitivity, and CDR.

EM - SIPro/PIPro

- An issue with port names causing a crash with FEM simulations has been fixed.

Data Display

General

- Fixed a DDS crash caused by executing matrix equation with wrong array element. An error is issued when the dimension specification mismatches the data when concatenating expressions.

- Fixed unexpected outlying points in a contour Description. The handling of invalid data points when slicing data is improved.

- Fixed an unexpected AEL error when double-clicking a re-ordered trace in Description Traces and Attributes dialog.

- Fixed issues related to Datasets getting stale. Datasets are properly updated after unexpected disconnection taking place between Data Display and simulation.

- Fixed the performance degradation of spline interpolate calculation.

Data Viewing & Analysis and Manipulation

- Marker's Sweep Index Equations get properly updated after the marker name is modified. For more information, refer to Marker's Sweep Index Equations documentation.

Power Electronics

General

- An issue has been fixed that could cause a crash of the Broadband Spice Model Generator.

Design Cloud

General

- Design Cloud ADS Sim: The simulator doesn't find the em-model file when checked in under Cliosoft. Background-When the user checks in an em-model under the `Cliosoft` server (cache enabled server), the em-model files present under `library>cell` are converted to symlinks whose paths point to `cliosoft cache` dir. Note that the files under the cache get renamed in this process. The netlist generated now has reference to the absolute path of the em-model file, which is under the cache directory. While simulating such a design, the simulator cannot find the dependent files because the em model expects the correct file names of its dependent files. To solve such scenarios, the netlist will contain the absolute path of the em-model file.

- Batch Simulation with emModel over Design Cloud fails with subprocess and parallel jobs. Circuits that call the em-model file are located when a user attempts to sweep the simulation using BatchSim with UseSeperateProcess = Yes.

- Failure in merging datasets from subjobs when using Pin Currents. An issue is resolved where a user saving Pin Currents in the output dataset would cause an intermittent failure in merging the datasets of different subjobs.

- Design Cloud ADS Sim: Unable to process comments that end with an escaped newline. Netlists that contain comments that end with escaped newline are supported.

Keysight's PathWave, an open, scalable, and predictive software platform, offers fast and efficient data processing, sharing and analysis at every stage in the product development workflow. Combining design software, instrument control and application-specific test software, it enables engineers to address increasing design, test, and measurement complexity and develop optimal electronic products.

PathWave Advanced Design System (ADS)is the world's leading electronic design automation software for RF, microwave, and high-speed digital applications. ADS pioneers the most innovative and powerful integrated circuit-3DEM-thermal simulation technologies used by leading companies in the wireless, high-speed networking, defense-aerospace, automotive and alternative energy industries. For 5G, IoT, multi-gigabit data link, radar, satellite and high-speed switched mode power supply designs, ADS provides an integrated simulation and verification environment to design high-performance hardware compliant with the latest wireless, high speed digital and military standards.

PathWave ADS 2023 Update 2.0includes new capabilities and enhancements for RF/MW, High Speed Digital, Power and Quantum Electronics in Python automation, design management, layout, data display, verification, circuit-EM simulation, high-performance-computing (HPC) and license queuing.

PathWave ADS 2023 High Speed Digital Latest Design Innovations You Shouldn't Miss

This video provides an overview of some of the latest design innovations for High-Speed Digital designers using Pathwave Advanced Design System (ADS) 2023 including Memory Designer, SerDes design, and PIPro design innovations.

Keysight Technologies Inc.is the world's leading electronic measurement company, transforming today's measurement experience through innovations in wireless, modular, and software solutions. With its HP and Agilent legacy, Keysight delivers solutions in wireless communications, aerospace and defense and semiconductor markets with world-class platforms, software and consistent measurement science. The company's nearly 10,500 employees serve customers in more than 100 countries.

Buy Premium From My Links To Get Resumable Support,Max Speed & Support Me

Rapidgator

http://peeplink.in/e0517f95e94c

Password peeplink: 123

Uploadgig

djqag.SETUP.part1.rar

djqag.SETUP.part2.rar

djqag.SETUP.part3.rar

djqag.SETUP.part4.rar

NitroFlare

djqag.SETUP.part1.rar

djqag.SETUP.part2.rar

djqag.SETUP.part3.rar

djqag.SETUP.part4.rar

Links are Interchangeable - Single Extraction

Free Download PathWave Advanced Design System (ADS) 2023 Update 2 (x64) is known for its high-speed downloads. It uses multiple file hosting services such as Rapidgator.net, Nitroflare.com, Uploadgig.com, and Mediafire.com to host its files